先进封装四要素:Wafer、Bump、RDL和TSV

什么是先进封装?我们先来看一下先进封装的定义和特点,先进封装就是采用了先进的设计思路和先进的集成工艺,对芯片进行封装级的重构,并且能有效提高系统功能密度的封装,我们称之为先进封装。先进封装这个词现在非常热门,它的英文称为Advanced Package,有时候也被称为高密度先进封装HDAP,是当前封装技术发展的热点。从晶圆厂到封装再到系统,整个半导体业界都很关注。

C大家可以想象一下,如果我们将这四要素想象成一座城市的基础建设,其中Wafer好比城市的地基,它是制造芯片的基本材料。晶圆是薄片状的硅片,所有的建筑(芯片)都是在这个地基上建造的,好的地基能够保证城市(芯片)的稳定性和长久耐用性。Bump是一种微小的连接点,负责将芯片和封装基板连接起来。想象一座城市中的桥梁,它把不同区域的建筑(芯片和封装基板)连接在一起,让信息可以顺利从一个地方传递到另一个地方。RDL 就像城市的道路网络,它是用来重新连接、分配信号路径的。想象一下,一座城市中有许多建筑(芯片),这些建筑之间需要有通道相互沟通。RDL 就是这些通道,它把各个建筑(芯片)的信号重新布线,让信息可以在不同建筑之间顺畅传递。TSV 是一种通过硅片垂直打通的技术,可以把信息从芯片的底层传递到上层,就像一座高层建筑里的电梯,帮助人和货物快速在不同楼层之间移动。TSV 使得芯片内部的数据传输更加高效、快捷,就像电梯让你不用爬楼梯一样,直接上下楼。它能够大大减少信号延迟,就像乘电梯比爬楼梯快多了。

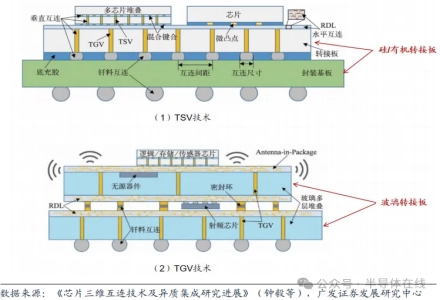

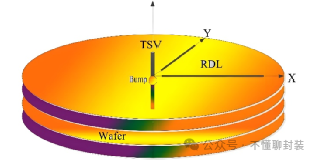

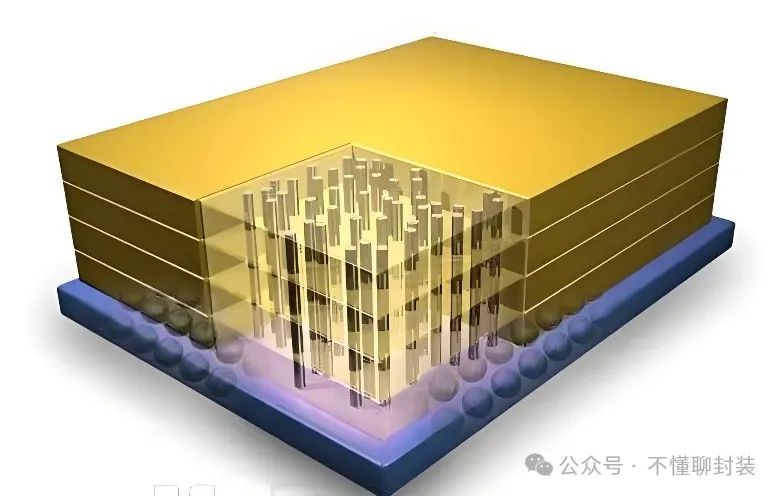

下图展示了先进封装四大要素的关系:RDL 负责在 平面上扩展电路,TSV 实现 Z 轴上的垂直电气互连,Bump 连接芯片和封装界面,而 Wafer 则作为集成电路的基础载体,接下来将分别对这四大要素进行详细介绍。

Wafer

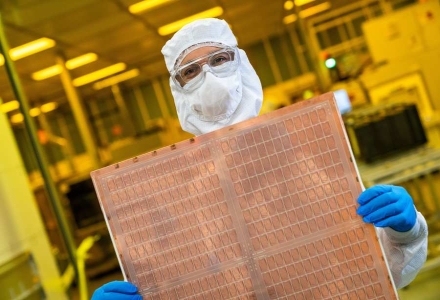

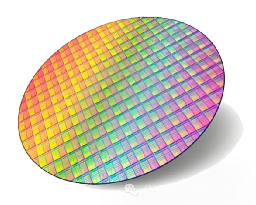

Wafer(晶圆)是半导体行业的核心基础材料,它是制造集成电路(IC)的平台。简单来说,Wafer 就像是电子元件的“基石”,所有的芯片电路都在这片薄薄的硅片上进行加工和形成。每一个芯片(Die)都是从 Wafer 上切割下来的,因此 Wafer 的质量和尺寸直接影响到最终芯片的性能和良率。

半导体 Wafer 的发展始于 20 世纪 50 年代,当时首批晶圆使用的是锗材料。然而,随着技术的进步,硅逐渐取代锗成为最主要的半导体材料,因为硅具有优异的半导体特性、丰富的资源以及相对容易加工的特性。

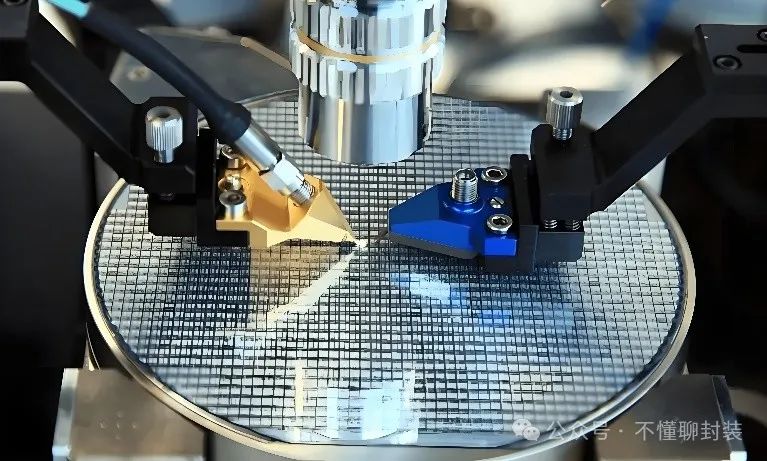

Wafer 的尺寸(直径)随着工艺的进步不断扩大。最早期的 Wafer 直径只有几英寸,而现代的 Wafer 已经达到了 300mm(12 英寸)甚至正在开发中的 450mm(18 英寸)。随着 Wafer 直径的增加,可以在一片 Wafer 上加工的芯片数量也相应增加,从而提高了生产效率并降低了成本。

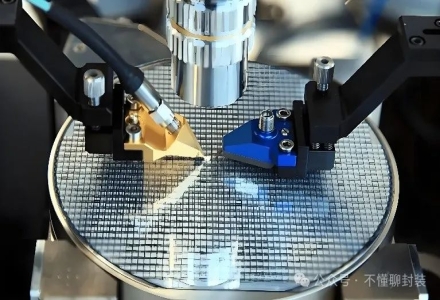

随着芯片尺寸的不断缩小和集成度的提高,对 Wafer 纯度的要求越来越高。现代晶圆几乎是纯硅材料,杂质含量极低(通常在十亿分之一以下)。此外,晶圆的晶体结构需要非常完美,以避免在制造过程中产生缺陷。为了满足这些要求,晶圆的制造需要在高度控制的环境下进行,包括生长单晶硅棒、切割、抛光和清洗等一系列复杂工艺。

除了传统的硅晶圆,其他材料的晶圆也逐渐进入半导体制造领域。例如,化合物半导体材料(如氮化镓 GaN 和碳化硅 SiC)晶圆在高频和高功率电子器件中得到了应用。这些材料具有硅无法比拟的优异性能,适用于特定的高端应用场景,如 5G 通信、射频器件和电动汽车。

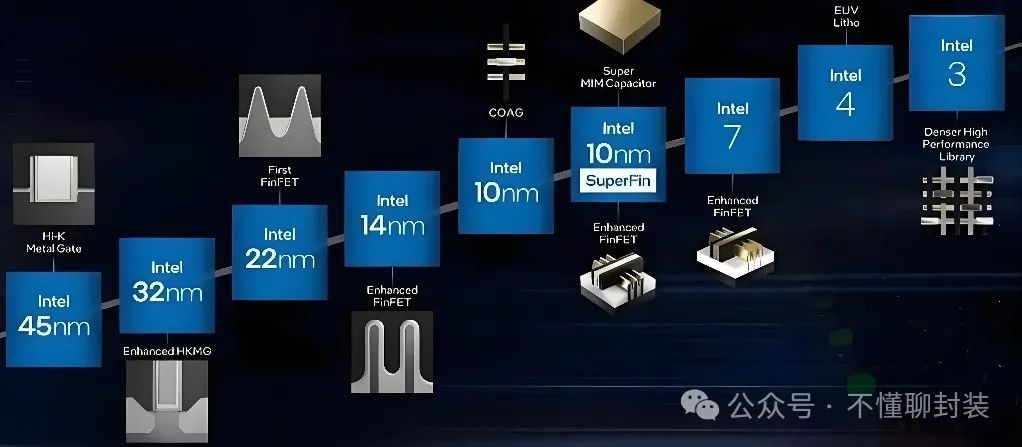

晶圆制造工艺正在不断向更小的节点(如 3nm、2nm)发展。这要求 Wafer 的纯度、平整度和结构缺陷控制达到极高水平。为了应对芯片复杂性和性能需求的增长,异质集成和 Chiplet (详细介绍可以看上一期介绍)技术逐渐兴起。这些技术依赖于不同类型的 Wafer(如硅基和化合物半导体基 Wafer)的结合,以实现高效能的芯片封装和集成。

Bump

在集成电路封装中,Bump 是一种微小的金属凸点,主要用于实现芯片与封装基板之间的电气连接和机械固定。它的主要作用类似于桥梁,确保芯片与基板之间的信号传输稳定,同时提供必要的物理支撑。

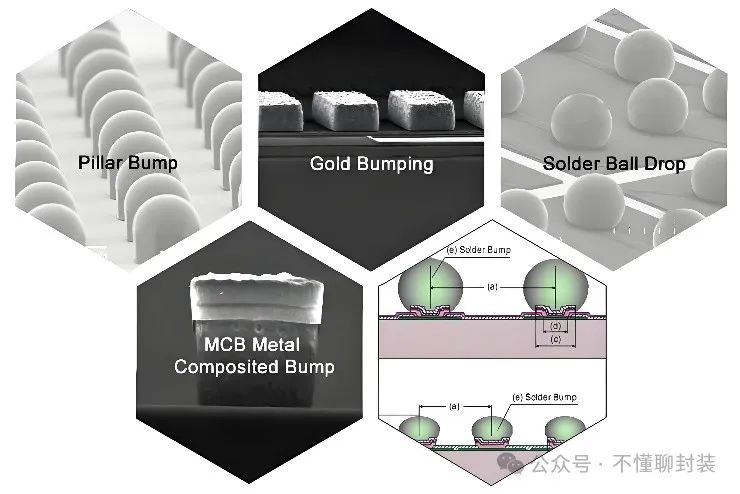

最早的 Bump 技术可追溯到 1960 年代,当时 IBM 发明了称为 C4(Controlled Collapse Chip Connection)的技术。这种技术通过将锡铅合金凸点置于芯片的焊盘上,然后将其翻转并焊接到基板上。这一过程被称为“翻转芯片”技术,是现代 Bump 技术的前身。

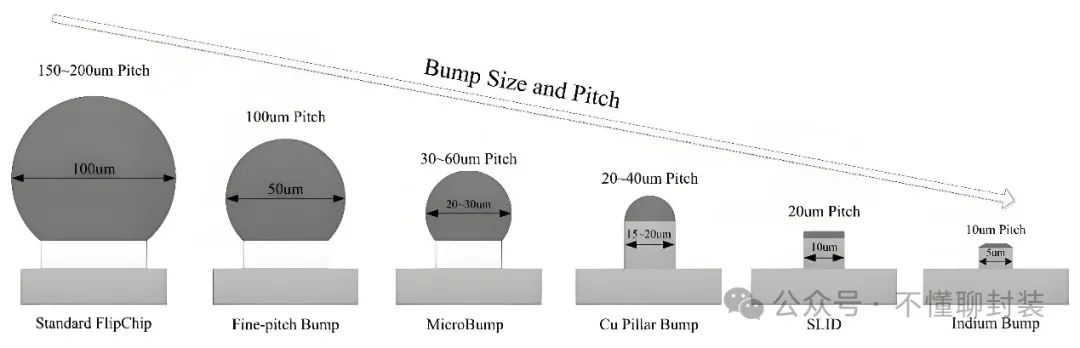

随着电子产品的微型化和集成度的提高,Bump 技术经历了材料与形态的多次演变。最初的锡铅合金逐渐被环保的无铅材料(如锡银铜合金)所取代。此外,随着芯片尺寸的缩小,Bump 的尺寸也越来越小,从最早的几百微米逐渐缩小到几十微米甚至更小。

近年来,随着对更高性能、更小尺寸的需求,Bump 技术进一步发展。例如,铜柱 Bump 技术逐渐取代了传统的球形 Bump 技术。铜柱 Bump 在提供更小尺寸、更高电流承载能力的同时,也具备更好的机械强度和热性能,适用于高性能计算芯片和移动设备。

目前,Bump 的尺寸和间距(Pitch)已经达到了微米级别,这使得高密度封装成为可能。更小的 Bump 和更密集的排列,有助于提升芯片的集成度和性能。随着不同应用需求的出现,Bump 的材料和结构也更加多样化。例如,高性能计算和服务器芯片通常采用铜柱 Bump,而移动设备和消费电子产品则更多采用锡银铜合金 Bump。此外,倒装芯片技术的广泛应用,也推动了不同类型 Bump 的发展。

RDL

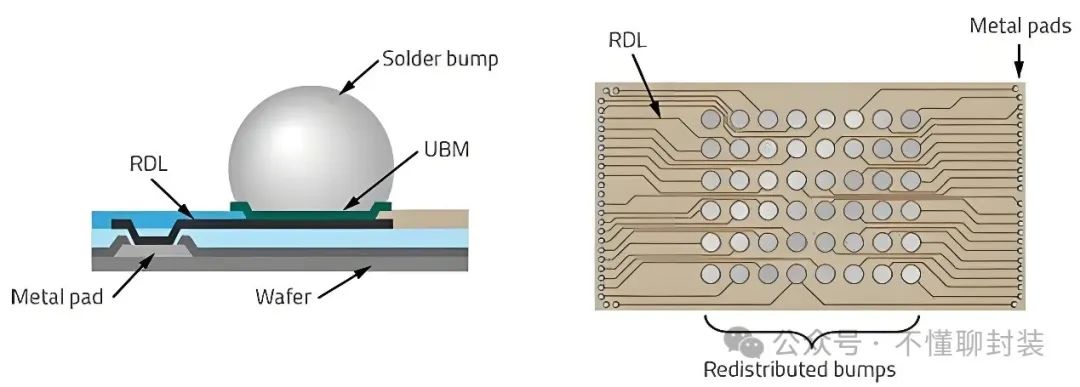

RDL(Redistribution Layer,重布线层)是在芯片封装中用于重新分配电气信号的金属层。它的主要作用是将芯片上的原始引脚重新布线,以便与封装基板或其他芯片进行更有效的电气连接。RDL 就像是道路网络,能够将芯片的输入/输出(I/O)引脚从密集区域重新分布到较大区域,从而实现更高效的连接方式。

RDL 技术最早应用于倒装芯片(Flip Chip)封装中,以解决传统芯片封装中引脚密度不够的问题。通过在芯片表面添加一层或多层金属布线,可以将芯片内部的电信号重新分布,突破了传统封装中引脚密度的限制。

早期的 RDL 技术主要使用简单的单层布线,适用于低引脚数的芯片。随着半导体工艺的进步和芯片集成度的提升,RDL 技术逐渐发展出多层布线结构,能够支持更复杂的信号传输和更高的引脚密度。

针对工艺要求的提高,RDL 使用的材料也从传统的铝和铜逐渐演变为更先进的材料组合,例如含有高导电性的铜和具有优异绝缘性能的聚酰亚胺(PI)或环氧树脂(Epoxy)等材料。这些材料的选择直接影响到 RDL 的导电性、机械强度和可靠性。

RDL 技术如今已经广泛应用于多种先进封装形式中,如倒装芯片(Flip Chip)、晶圆级封装(WLP)、扇出型封装(Fan-Out Packaging)等。特别是在移动设施、可穿戴设备、高性能计算等领域,RDL 技术能够有效支持芯片的小型化和高性能。目前,RDL 的布线层数可以达到多层结构,甚至可以支持 3D 封装中的垂直互连。这种高密度多层 RDL 可以进一步提高封装的集成度,使得在有限的封装空间内实现更复杂的功能。这对于先进的处理器、AI 芯片以及其他高性能计算芯片尤为重要。

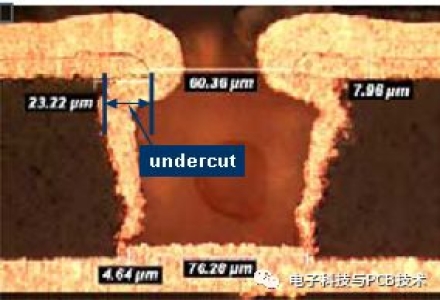

随着芯片制程工艺的不断缩小,RDL 的布线宽度和间距也在不断缩小。例如,RDL 的线宽已经可以达到 1 微米甚至更小,以支持先进制程节点(如 5nm、3nm)的封装需求。同时,RDL 的制造工艺也越来越精细,包括光刻、电镀、刻蚀等多个步骤,确保在微米级甚至纳米级别的精度下完成高质量的布线。未来,RDL 技术在材料和工艺上的创新将继续推进。例如,可能会出现更加导电、更加柔韧的材料来提高 RDL 的可靠性和适应性。同时,更加精细的制造工艺也将推动 RDL 技术向更高密度、更小尺寸发展。

TSV

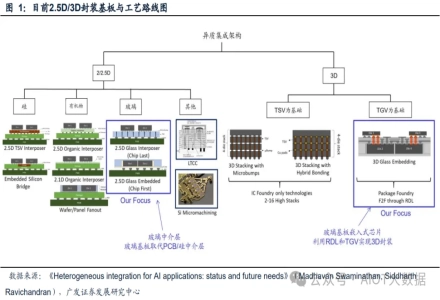

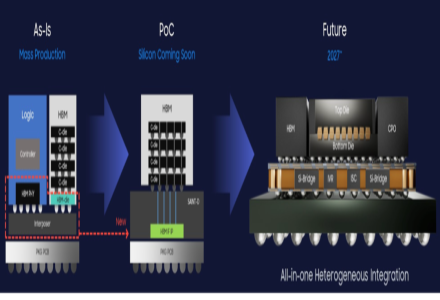

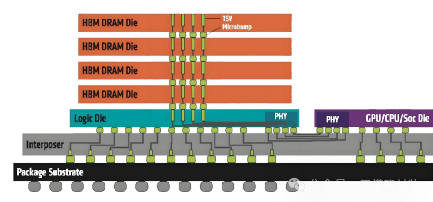

TSV可以分为2.5D TSV和3D 芯片TSV堆叠,其中2.5D TSV使用了转接板(Interposer)作为连接多个芯片(如处理器和内存)的平台。这些芯片通过TSV在中介层上进行连接,而不是直接堆叠在一起。大家可以把2.5D TSV想象成一个多层蛋糕,其中每层蛋糕(芯片)都不直接叠在一起,而是放在一个多孔的蛋糕托盘(转接板)上。蛋糕托盘的孔洞(TSV)帮助每层蛋糕与其他层进行信息传递。

而3D TSV是一种在半导体器件中垂直穿过硅片的电连接技术,主要用于3D集成电路(3D IC)和3D封装中。TSV允许芯片之间直接进行垂直连接,而不需要传统的平面布线,从而实现更高的互连密度、更快的信号传输速度和更低的功耗。想象一下,传统的芯片就像是一本厚厚的书,每一页都必须通过书边的纸张(即外部互连)来与其他页面进行信息交换。而TSV的出现则相当于在书的中间打洞,每一页都能直接通过这个洞与其他页直接通信。这种直接连接不仅大大缩短了信息的传输距离,还减少了信号延迟和功耗。

TSV 技术的概念最早在 20 世纪 80 年代提出,但直到 2000 年代初期才开始在半导体行业中得到广泛关注。随着摩尔定律的推进和芯片集成度的提升,平面工艺的空间逐渐被耗尽,业界开始寻求通过垂直集成来进一步提升性能和功能密度。TSV 技术成为这一过程中最重要的突破口之一。尽管 TSV 技术有着巨大的潜力,但其工艺实现却面临诸多挑战,包括精确的深孔刻蚀、填充材料的选择、热应力管理、孔与孔之间的电气隔离等。为了克服这些挑战,半导体制造商们投入了大量资源进行研发。如今,TSV 工艺已经相对成熟,能够实现高精度、高可靠性的垂直互连。

自其发展以来,TSV 技术在高性能计算、图像传感器、存储器等领域取得了显著进展。随着工艺的进步和市场需求的增长,TSV 的应用范围将进一步扩大,并在未来的先进封装技术中扮演更加重要的角色。

小结

现在对先进封装四大要素进行总结,四种不同的封装关键点的特点如下面表格所示。

先进封装关键要素 | 功能 | 应用 | 发展趋势 |

Wafer | 集成IC的载体 | 2D/2.5D/3D | 尺寸越大,精度越高 |

Bump | 芯片界面连接 | 2D/2.5D/3D | 尺寸越小,密度越高 |

RDL | 在平面扩展 | 2D/2.5D/3D | 尺寸越小,密度越高 |

TSV | 纵向延伸 | 2.5D/3D | 尺寸越小,密度越高 |

总的来说,Wafer、Bump、RDL和TSV是先进封装技术的四大基石,各自承担着关键功能。Wafer(晶圆)作为集成电路的载体,贯穿整个半导体制造过程;Bump(凸点)则确保了芯片与基板之间的可靠连接,广泛应用于倒装芯片和晶圆级封装中;RDL(重布线层)通过重新分配芯片的电气信号,支持高密度和高性能的封装;TSV(硅通孔)实现了垂直方向的电气互连,是2.5D和 3D 集成封装的核心。四者相互配合,共同推动了芯片封装的小型化、高密度和高性能化,并将在未来的半导体封装技术中继续发挥重要作用。

版权说明:本文转载自"不懂聊封装",出于非商业性的技术交流和科研之目的,并不意味着赞同其观点或证实其内容的真实性。如转载稿涉及版权等问题,请作者联系本网站管理人员,我们协调给予处理(或删除)。如不同意本网之转载,请及时告知本网撤除。